已知Cache命中率H=0.98,主存比Cache慢4倍,已知主存存取周期为200ns,则系统平均访问时间是______ns。

- A.50

- B.53

- C.100

- D.125

正确答案及解析

正确答案

B

解析

本题考查计算机Cache基础知识。高速缓冲存储器(Cache)最重要技术指标是命中率。CPU在Cache中找到有用数据被称为命中,当Cache中没有CPU所需数据时(这时称为未命中),CPU才访问内存。为了保证CPU访问时有较高命中率,Cache中内容应该按一定算法替换。一种较常用算法是“最近最少使用算法”(LRU算法),它是将最近一段时间内最少被访问过行淘汰出局。因此需要为每行设置一个计数器,LRU算法是把命中行计数器清零,其他各行计数器加1。当需要替换时淘汰行计数器计数值最大数据行出局。这是一种高效、科学算法,其计数器清零过程可以把一些频繁调用后再不需要数据淘汰出Cache,提高Cache利用率。当新主存块需要调入Cache并且它可用空间位置又被占满时,需要替换掉Cache数据,这就产生了替换策略(算法)问题。根据程序局部性规律可知:程序在运行中,总是频繁地使用那些最近被使用过指令和数据。这就提供了替换策略理论依据。替换算法目标就是使Cache获得最高命中率。Cache替换算法是影响代理缓存系统性能一个重要因素,一个好Cache替换算法可以产生较高命中率。主存存取周期为200ns,主存比Cache慢4倍,则Cache存取周期为50ns。Cache命中率为0.98,则系统平均访问时间是50×0.98+200×0.02=53ns。

你可能感兴趣的试题

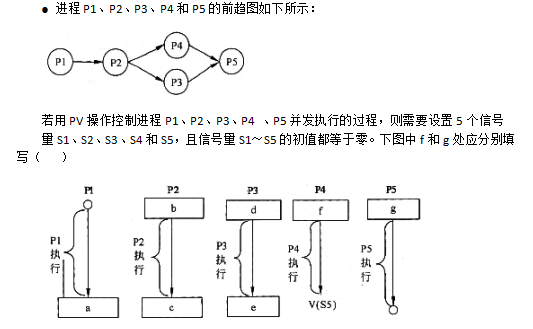

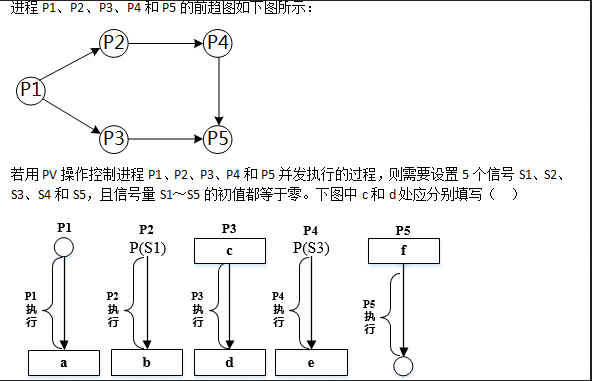

-

- A.V(S2)和P(S4)

- B.P(S2)和V(S4)

- C.P(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案

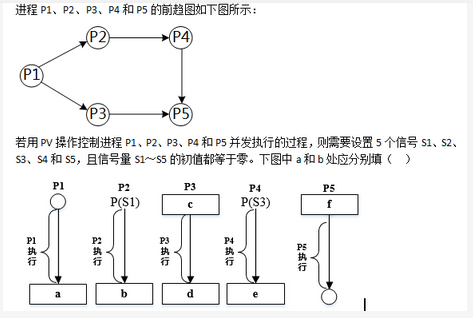

-

- A.V(S1)P(S2)和V(S3)

- B.P(S1)V(S2)和V(S3)

- C.V(S1)V(S2)和V(S3)

- D.P(S1)P(S2)和V(S3)

- 查看答案

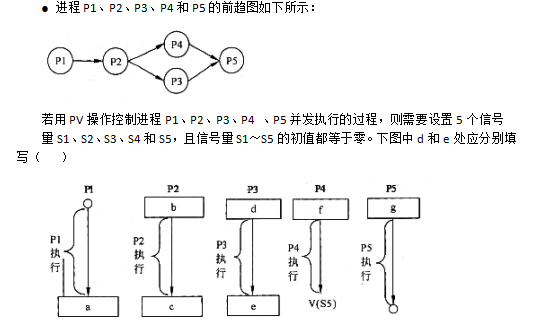

-

- A.P(S4)和V(S4)V(S5)

- B.V(S5)和P(S4)P(S5)

- C.V(S3)和V(S4)V(S5)

- D.P(S3)和P(S4)V(P5)

- 查看答案

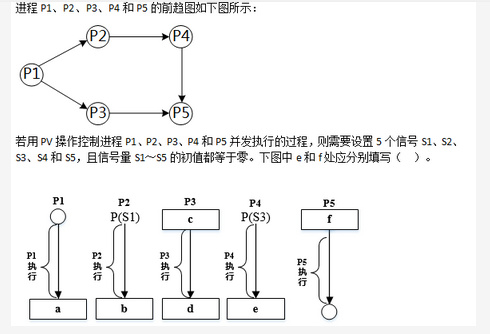

-

- A.P(S3)和V(S4)V(S5)

- B.V(S3)和P(S4)P(S5)

- C.P(S3)和P(S4)P(S5)

- D.V(S3)和V(S4)V(S5)

- 查看答案

-

- A.P(S2)和P(S4)

- B.P(S2)和V(S4)

- C.V(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案