在嵌入式系统硬件设计中,可以采用( )方法减少信号辐射。

- A.去掉芯片电源到地之间电容

- B.增加线长

- C.减小线宽

- D.在有脉冲电流引线上串小磁珠

正确答案及解析

正确答案

解析

本题考查嵌入式系统硬件设计基础知识。电磁干扰(EMI,Electro Magnetic Interference)可分为辐射和传导干扰。福射干扰就是干扰源以空间作为媒体把其信号干扰到另一电网络。而传导干扰就是以导电介质作为媒体把一个电网络上信号干扰到另一电网络。在高速系统设计中,集成电路引脚、高频信号线和各类接插头都是PCB板设计中常见辐射干扰源,它们散发电磁波就是电磁干扰(EMI),自身和其他系统都会因此影响正常工作。PCB板设计技巧中有不少解决EMI问题方案,例如:EMI抑制涂层、合适EMI抑制零件和EMI仿真设计等,主要方法包括:1.共模EMI干扰源(如在电源汇流排形成瞬态电压在去耦路径电感两端形成电压降)在电源层用低数值电感,电感所合成瞬态信号就会减少,共模EMI从而减少。可以通过减少电源层到IC电源引脚连线长度来降低该干扰。2.电磁屏蔽,尽量把信号走线放在同一PCB层,而且要接近电源层或接地层。3.零件布局(布局不同都会影响到电路干扰和抗干扰能力)中根据电路中不同功能进行分块处理(例如解调电路、高频放大电路及混频电路等),在这个过程中把强和弱电信号分开,数字和模拟信号电路都要分开,各部分电路滤波网络必须就近连接,这样不仅可以减小幅,还可以提高电路抗干扰能力,减少被干扰机会。4.布线考虑(不合理布线会造成信号线之间交叉干扰)不能有走线贴近PCB板边框,以免于制作时造成断线。电源线要宽,环路电阻便会因而减少。信号线尽可能短,并且减少过孔数目。拐角布线不可以用直角方法,应以135°角为佳。数字电路与模拟电路应以地线隔离,数字地线与模拟地线都要分离。在电源和地之间加电容、减少线长、增加线宽;可以在有脉冲电流引线上串小磁珠。

你可能感兴趣的试题

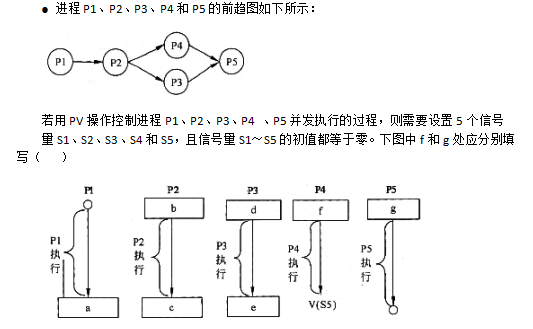

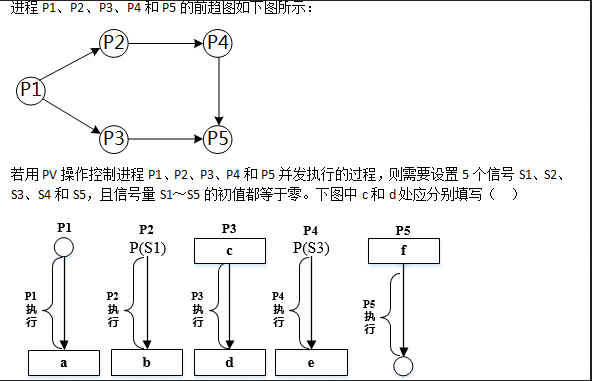

-

- A.V(S2)和P(S4)

- B.P(S2)和V(S4)

- C.P(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案

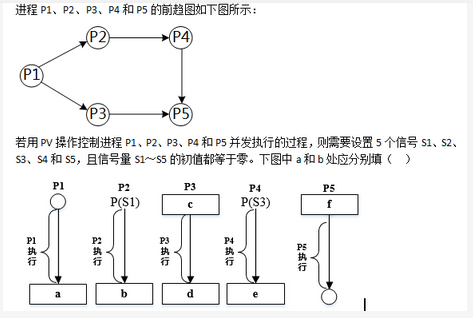

-

- A.V(S1)P(S2)和V(S3)

- B.P(S1)V(S2)和V(S3)

- C.V(S1)V(S2)和V(S3)

- D.P(S1)P(S2)和V(S3)

- 查看答案

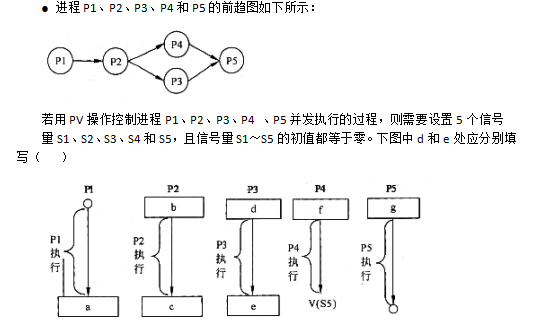

-

- A.P(S4)和V(S4)V(S5)

- B.V(S5)和P(S4)P(S5)

- C.V(S3)和V(S4)V(S5)

- D.P(S3)和P(S4)V(P5)

- 查看答案

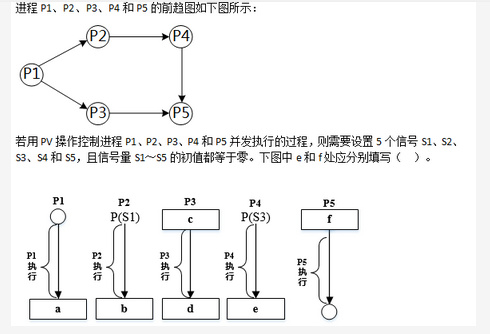

-

- A.P(S3)和V(S4)V(S5)

- B.V(S3)和P(S4)P(S5)

- C.P(S3)和P(S4)P(S5)

- D.V(S3)和V(S4)V(S5)

- 查看答案

-

- A.P(S2)和P(S4)

- B.P(S2)和V(S4)

- C.V(S2)和P(S4)

- D.V(S2)和V(S4)

- 查看答案